I transistor sono tra i componenti più usati nell'elettronica digitale, un componente che ha rivoluzionato il mondo dell'elttronica e dell'informatica. I processori dei computer, dei telefoni, dei nostri elettrodomestici, delle macchine, degli aerei e di qualsiasi cosa digitale sono fatti di reti logiche implementate con milioni e nei processori più nuovi, miliardi di transistor.Vediamo come funzionano e come si progetta una piccola rete logica seguendo la logica CMOS e la PASS TRANSISTOR. Analizziamo i transistor MOSFET((Metal Oxide Semiconductor Field Effect Transistor), uno dei tipi di transistor più usati e più importanti.

Introduzione ai Transistor ⚙️

Un transitor è come un interruttore elettronico, un componente che può essere acceso o spento, un componente che può essere usato per memorizzare informazioni, per fare calcoli e implementare reti logiche.

Per affrontare l'argomento è necessario sapere cos'è una porta logica.Consiglio di vedere le porte NOT,AND,NAND,XOR,NOR,XNOR.

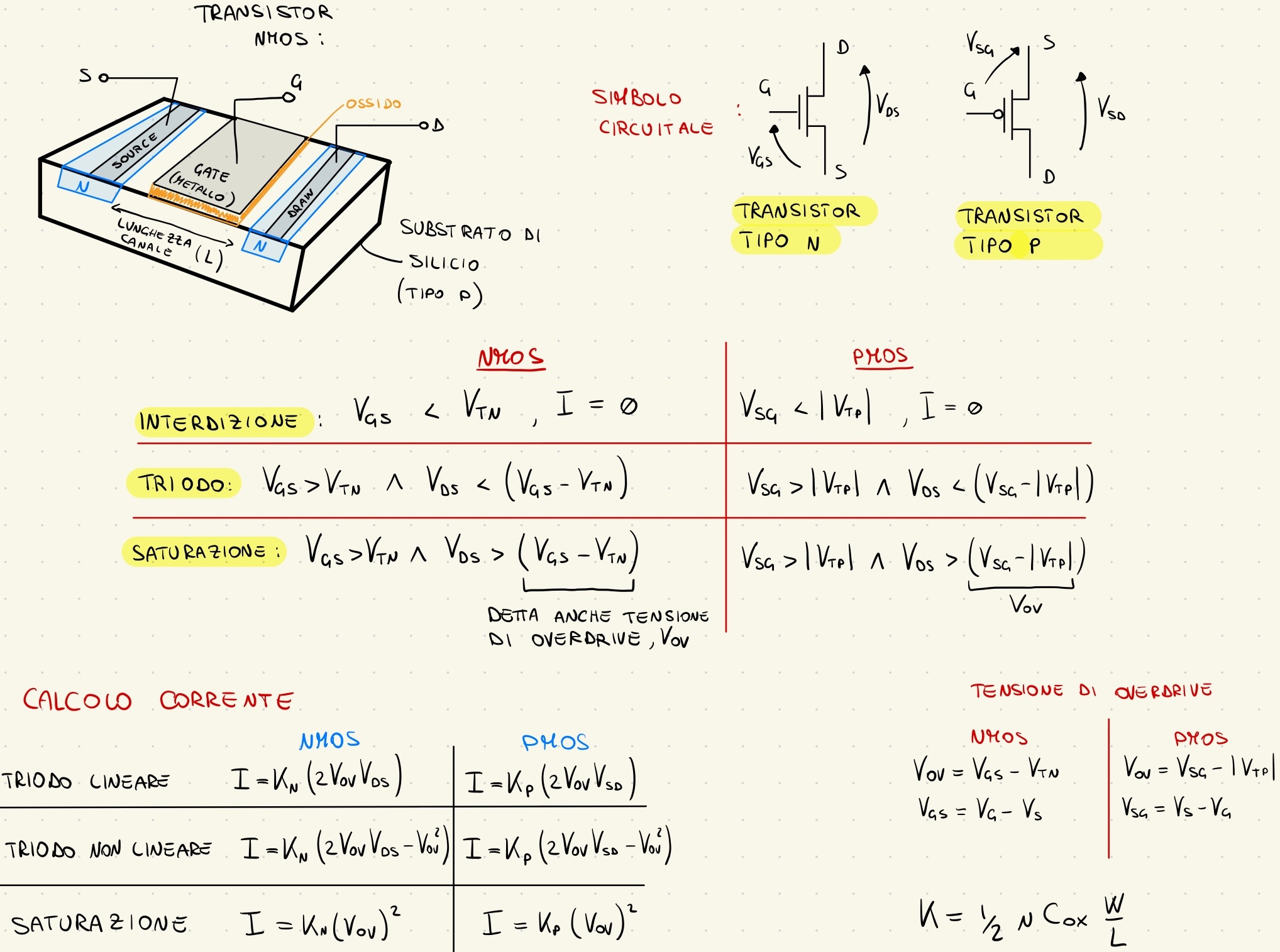

Ci sono due tipi di transistor, quelli a canale p e quelli a canale n.Consideriamo per il momento che è un interruttore che ha 3 terminali, uno è chiamato source, uno gate, e uno drain. Quello di drain è l'input, cioè ciò che controlla questo interruttore.

Il transistor MOSFET è un dispositivo formato da una "fetta" di semiconduttore(silicio) detta substrato, su cui sono create due regioni di tipo opposto, il source e il drain, e una regione di tipo opposto, il gate,al centro. Il gate è separato però dal substrato con un ossido, una specie di dielettrico dei condensatori,

infatti substrato+ossido+gate formano un condensatore, che è il cuore del transistor MOSFET, il condensatore MOS.

Il gate è collegato a un elettrodo di controllo, che può essere portato a una tensione positiva o negativa per controllare la corrente che scorre tra il source e il drain.In base alla tensione che forniamo al gate, avremo una corrente che scorre o meno nel transistor.La tensione ai suoi capi rimane invece quella che diamo al source e al drain.Quindi l'input è il gate e l'output è il source e il drain(la corrente che scorre tra loro).

Vediamo cosa fa un NMOS: se il gate ha 0V non scorre corrente tra drain e source(il nostro output), se ha 5V ad esempio,scorrerà una corrente tra D e S.

Il concetto di base è questo: consideriamo un NMOS, noi vogliamo implementare una porta logica e sappiamo bene che queste funzionano con valori booleani, cioè solo con due valori, 0 o 1. Il concetto del nmos è che se il suo input è 0 l'output è 0 e se l'input è 1 l'output è 1. Quindi se il gate è a 0V non scorre corrente tra D e S, se è a 5V scorre corrente tra D e S.Al contrario, nel pmos, se l'input è 1 l'output è 0 e se l'input è 0 l'output è 1.

Ora però dobbiamo ricordarci che siamo in un mondo fatto da valori analogici, quindi non possiamo avere un gate a 0V o 5V, ma possiamo avere un gate a 0.1V,0.9V,1V,3V,ecc... Quindi dobbiamo definire quale tensione corrisponde al nostro 1 logico e allo 0 logico.Dobbiamo poi definire una tensione di soglia, una tensione che se superata, il transistor nmos ad esempio si accende, se non superata, il transistor si spegne.

Definiamo allora il nostro 1 logico come la tensione Vdd, cioè la tensione di alimentazione del circuito(dei valori tipici sono 3.3V o 5V) e il nostro 0 logico come la tensione di massa, cioè 0V.Poi definiamo la soglia logica, Vth, un buon valore è Vdd/2, perchè ci garantisce una buon margine di rumore(vedremo in seguito cos'è).Se ad una porta logica diamo in ingresso questo valore, Vth, in uscita avremo esattamente Vth, cioè un valore indefinito, perchè non è nè 0 nè 1, quindi non è un valore logico.

Ogni transistor ha una sua tensione di soglia Vt(Vtn per gli nmos e Vtp per i pmos), da non confondere con la tensione di soglia logica Vth.Questa è la tensione che deve superare il gate(o meglio tensione gate-source) per far scorrere corrente tra source e drain.

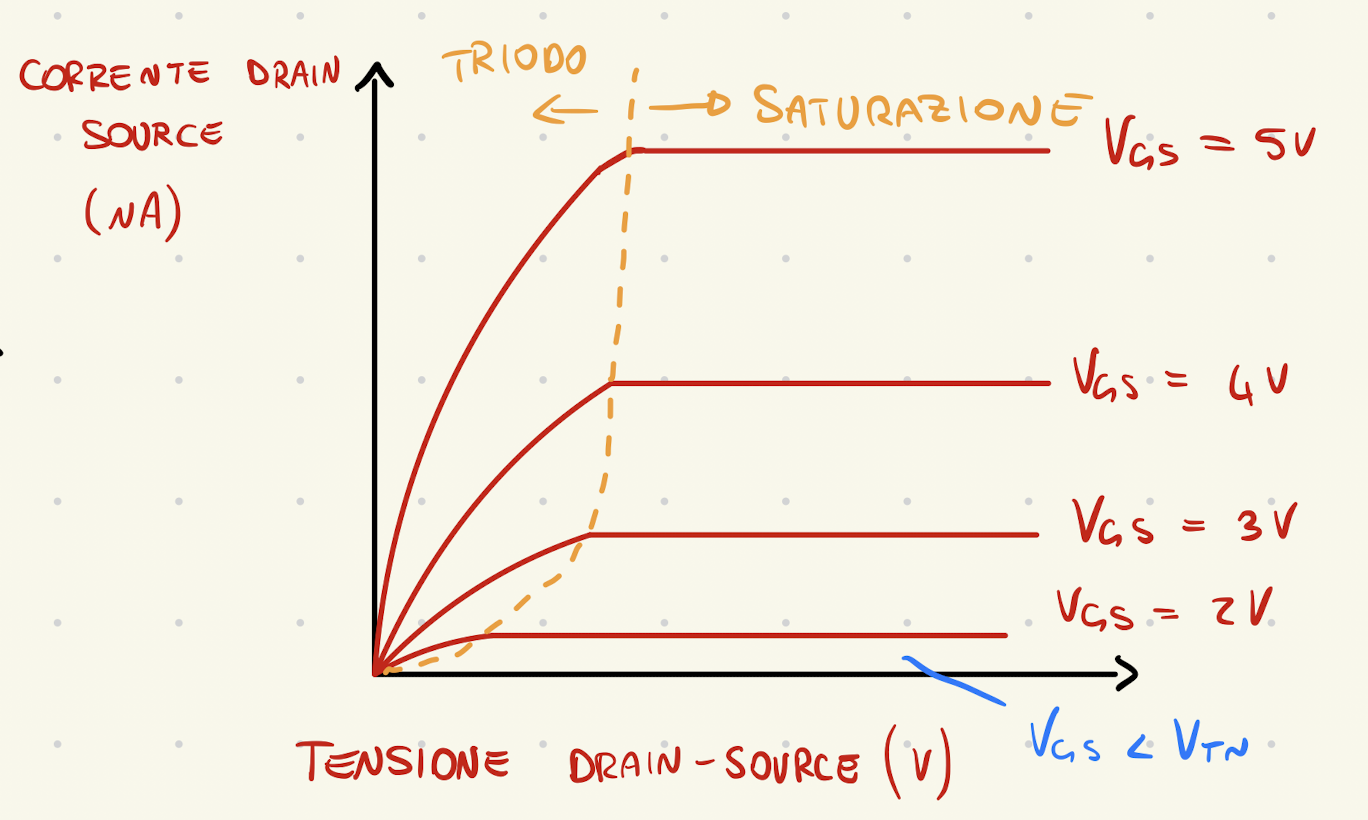

Ogni transistor ha 3 zone di funzionamento:

•Zona di Interdizione quando la tensione gate source è inferiore a Vtn o Vtp: non scorre corrente, transistor spento

•Zona di Triodo(Lineare quando la tensione di gate source è vicina a Vtn o Vtp e Non Lineare fino a un valore detto Vov):scorre corrente(ma dipende dalla Vds o Vsd applicata)

•Zona di Saturazione quando la tensione gate source è maggiore della Vov(detta tensione di overdrive):scorre corrente costante

nb: ho detto tensione gate source facendo riferimento al nmos, ma per i pmos si deve invertire, cioè Vsg = Vs-Vg, cioè tensione al source meno tensione al gate(perchè il pmos come abbiamo già detto funziona al contrario, si accende quando non c'è tensione al gate e si spegne quando c'è una tensione che supera Vtp).

Vediamo ora tutte le equazioni e espressioni che ci serviranno, con le relative equazioni della corrente di uscita(tra drain e source nel nmos e tra source e drain nel pmos).

Vtp è in genere indicata negativa, per cui nelle disequazioni si mette il modulo, in modo da lasciarle semplici e praticamente uguali per pmos e nmos(basta invertire Vgs con Vsg e Vds con Vsd).

k è una costante che dipende dal tipo di transistor, dalla tecnologia di fabbricazione, dalla temperatura, ecc... Più è alta e più il transistor è performante, quindi sarà in grado di far scorrere più corrente tra drain e source a pari tensione gate source.

Perchè interdizione, triodo e saturazione ? Perchè in triodo la corrente ha un andamento diverso ed è più basso e dipendente dalla tensione applicata tra drain e source.In saturazione invece è più alta, ha un valore costante nel tempo, non dipende più dalla tensione tra drain e source e dipende solo dalla tensione gate source.

La zona di triodo poi ha due sottozone, la lineare e la non lineare. In quella lineare il transistor si comporta come una resistenza, in quella non lineare come una resistenza variabile o anche come un generatore di corrente.Quando un transistor è acceso, la sua resistenza è circa 1/(2kVov)

nella realtà però in saturazione non è proprio costante, ma ha un andamento leggermente crescente, ma trascurabile, dovuto a un effetto detto modulaione di lunghezza del canale, che non ci interessa per ora.

Infine, quando connettiamo due transistor in serie o in parallelo con lo stesso gate, otteniamo un transistor equivalente(si semplificano quindi come per le resistenze):

•Connessione in Serie: otteniamo un transistor con una Keq = k1+k2

•Connessione in Parallelo: otteniamo un transistor con una Keq = (k1*k2)/(k1+k2).

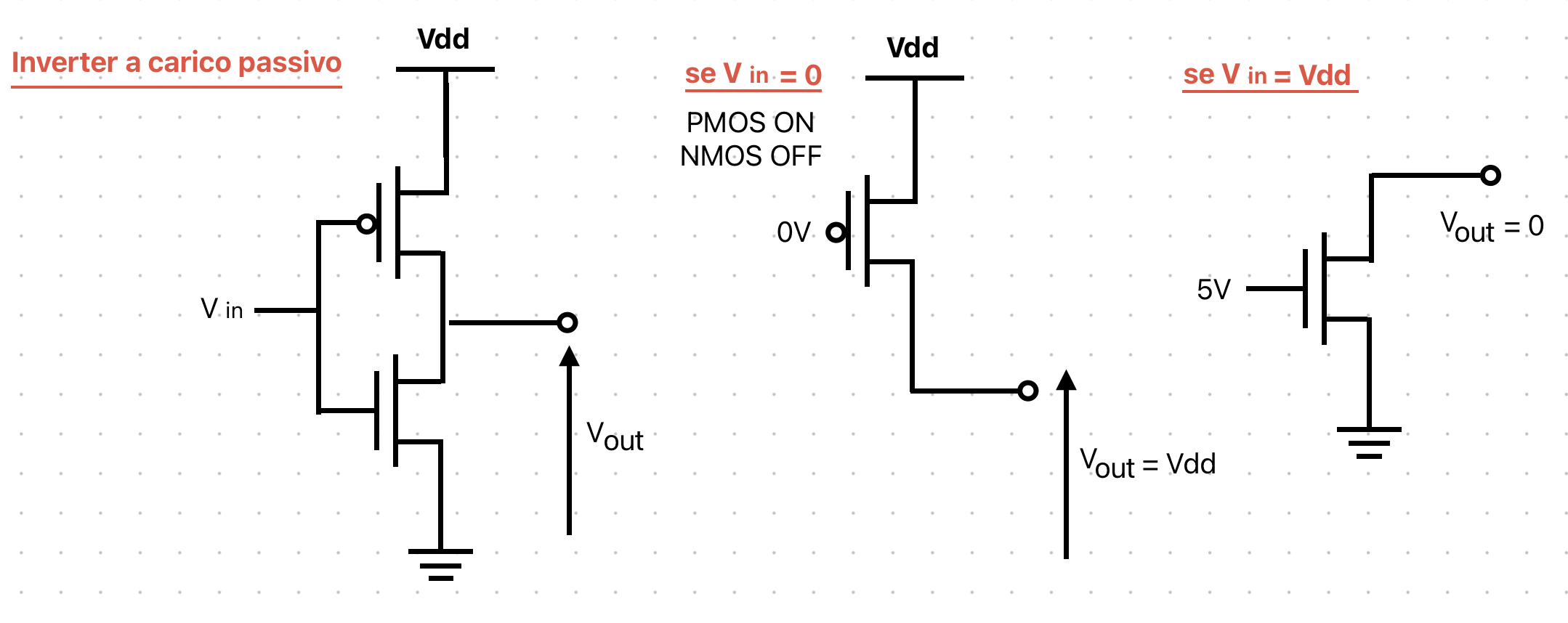

Inverter a Carico Passivo e CMOS

Vediamo ora come applicare quello che abbiamo imparato fin ora per costruire una porta logica NOT, o inverter, quindi una porta logica costituita da un solo segnale di input e un solo segnale di output. Inverte l'input che gli viene passato: se passo 1 in uscita ho 0, se passo 0 in uscita ho 1.E' una delle porte logiche più importanti e tra le più usate, è una di quelle fondamentali.

Serve per fare tutte le altre porte logiche.

Come fanno i computer a salvare e visualizzare immagini? Come fanno a riprodurre suoni? Come fanno a fare le operazioni che normalmente facciamo? Come fanno a interpretare i nostri comandi? Questo è possibile grazie alle reti logiche dei processori, fatte di milioni di transistor. Le informazioni sono codificate in binario, cioè con 0 e 1. Quindi una foto(ma in generale qualsiasi informazione in un calcolatore) ad esempio corrisponde in memoria a una serie di transistor che hanno salvato sequenze lunghissime di 0 e 1, che rappresentano l'immagine, secondo una certa codifica.Ecco perchè le porte logiche sono cosi importanti.

Vediamo ora come costruire una porta NOT. Vedremo due modi, il primo, poco efficiente ma molto semplice è l'inverter con carico passivo, il secondo invece è più efficiente ma usa 2 transistor ed è l'invert CMOS.

L'inverter con carico passivo non è altro che una resistenza connessa al drain di un transistor nmos, il cui source è connesso a GND(massa). L'altro terminale della resistenza è connesso a Vdd(alimentazione).

L'uscita sarà presa tra la resistenza e il transistor, cioè sul terminale di drain.

Se Vin è 1 logico, ci aspettiamo di avere in uscita 0 logico, cioè 0V: quando Vin=Vdd il transistor è acceso ed equivale ad una resistenza(quando Vin=Vdd è molto bassa, infatti è trascurabile).Trascurando quindi la resistenza,la corrente scorre tutta nel transistor perchè è un percorso conduttivo diretto a massa, ricorda che la corrente "preferisce" scorrere nel percorso a minor resistenza e quindi è diretta a GND cosi che in uscita vedremo GND, cioè 0V.

Questo in realtà è un andamento ideale, perchè in realtà ha comunque un minimo di resistenza il transistor e quindi la vera Vout sarà un valore leggermente maggiore di 0V(ad esempio 0.02V), ma rimarrà sempre valore logico 0.Se vogliamo calcolare il vero valore di Vout quando Vin = Vdd, basta fare il partitore di tensione: Vout = Vdd*Ron/(Ron+R).

Se Vin è 0 logico, ci aspettiamo di avere in uscita 1 logico, cioè Vdd: quando Vin=0V il transistor è spento, quindi la corrente non scorre nel transistor, ma scorre tutta nella resistenza R, che è collegata a Vdd, quindi in uscita vedremo Vdd, cioè il nostro 1 logico.

Ecco un grafico che mostra l'andamento di Vout in funzione di Vin(caratteristica statica):

Idealmente ci aspettiamo un'onda quadra dalle porte logiche(quindi una porta che commuta istantaneamente da 0 a 1 o da 1 a 0, senza aspettare nessun tempo quindi), ma nel mondo reale, analogico, non è cosi, spesso i transistor creano delle capacità parassite, cioè è come se ci fossero dei condensatori e bisogna aspettare che si caricano per vedere l'uscita a 1 logico o che si scaricano per vederla a 0 logico.Questi tempi(generalmente molto molto piccoli,poi vedremo) sono detti tempi di propagazione e sono molto importanti per capire quanto è veloce un circuito, quanto è performante.

Questo inverter a carico passivo però ha un problema: la disspazione di potenza, troppo alta, a causa della presenza della resistenza in alto, infatti dissipiamo potenza anche quando l'input è 0V.

Qui facciamo una precisazione:

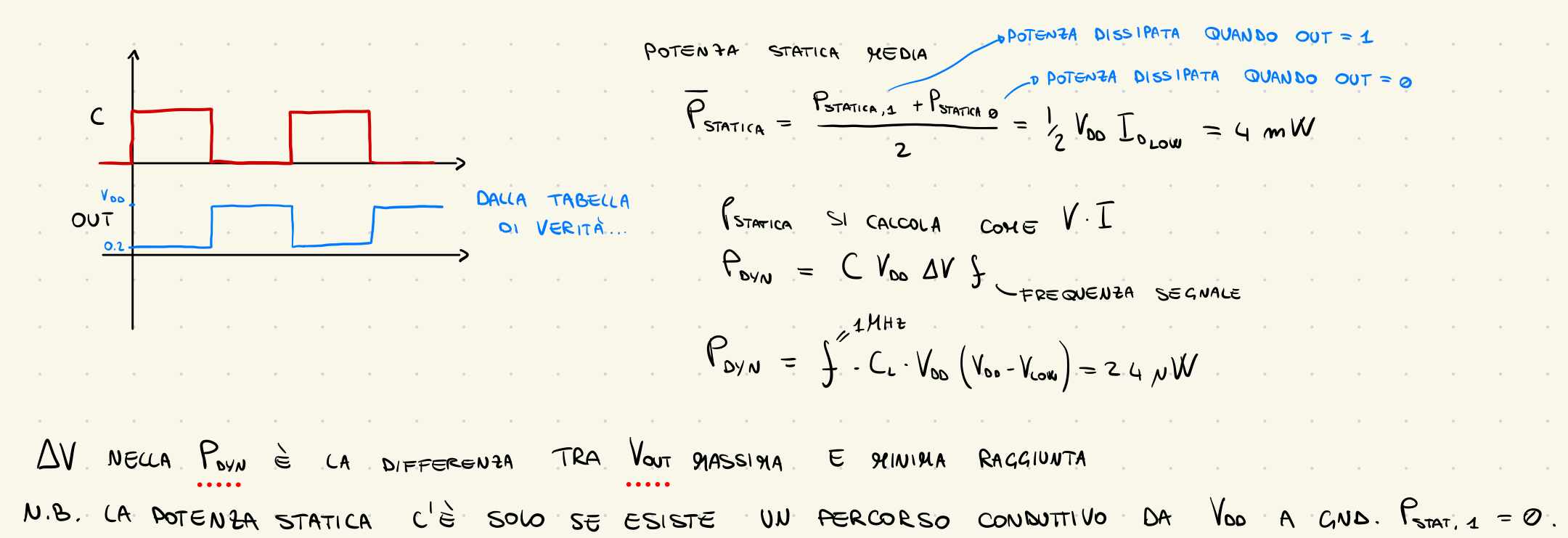

•Potenza Statica: potenza dissipata senza considerare le capacità, dovuta a percorsi conduttivi che vanno da Vdd a GND direttamente, infatti nelle reti CMOS vedremo che è zero perchè non c'è mai un percorso da Vdd a massa, ma è accesa o la rete di pull up o la rete di pull down(vedremo dopo di cosa si tratta).

•Potenza Dinamica: potenza dissipata a causa delle capacità parassite, dovuta a cariche che si spostano, a correnti che scorrono, a transistor che si accendono e si spengono.

In un esercizio del prossimo paragrafo vedremo in pratica questi due concetti e il calcolo dei tempi di propagazione.

Vediamo adesso un altro tipo di inverter, molto più efficiente in termini energetici, l'inverter CMOS.

Questo inverter è costruito prendendo un PMOS al posto della resistenza, connettendo quindi i due transistor, con un gate in comune:

Quindi qui abbiamo un transistor nmos e un transistor pmos, connessi tra loro, con un gate in comune. Se il gate è a 0V, il pmos è acceso e il nmos è spento, quindi in uscita avremo Vdd, cioè 1 logico. Se il gate è a Vdd, il pmos è spento e il nmos è acceso, quindi in uscita avremo 0 logico.

I più attenti si staranno chiedendo perchè non possiamo usare direttamente un pmos per fare un inverter...Possiamo farlo, ma avremmo un problema di prestazioni e di potenza dissipata: quando Vin= Vdd il pmos è spento e l'uscita rimane in uno stato indefinito, quindi dovrei usare una resistenza per forzare l'uscita a 0 e questo porta a dissipazione di potenza, tanto vale usare l'inverter visto prima allora. Un pmos e basta non posso usarlo perchè quando Vin =Vdd l'uscita rimarrebbe fluttuante, cioè con un valore logico indefinito.

L'inverter CMOS è molto più efficiente in termini energetici, infatti la potenza statica è zero, perchè non c'è mai un percorso conduttivo diretto da Vdd a GND, ma è sempre acceso o il pmos o l'nmos, quindi non c'è mai dissipazione di potenza statica.

Progetto Reti logiche in CMOS logic e PTL e calcolo tempi di propagazione

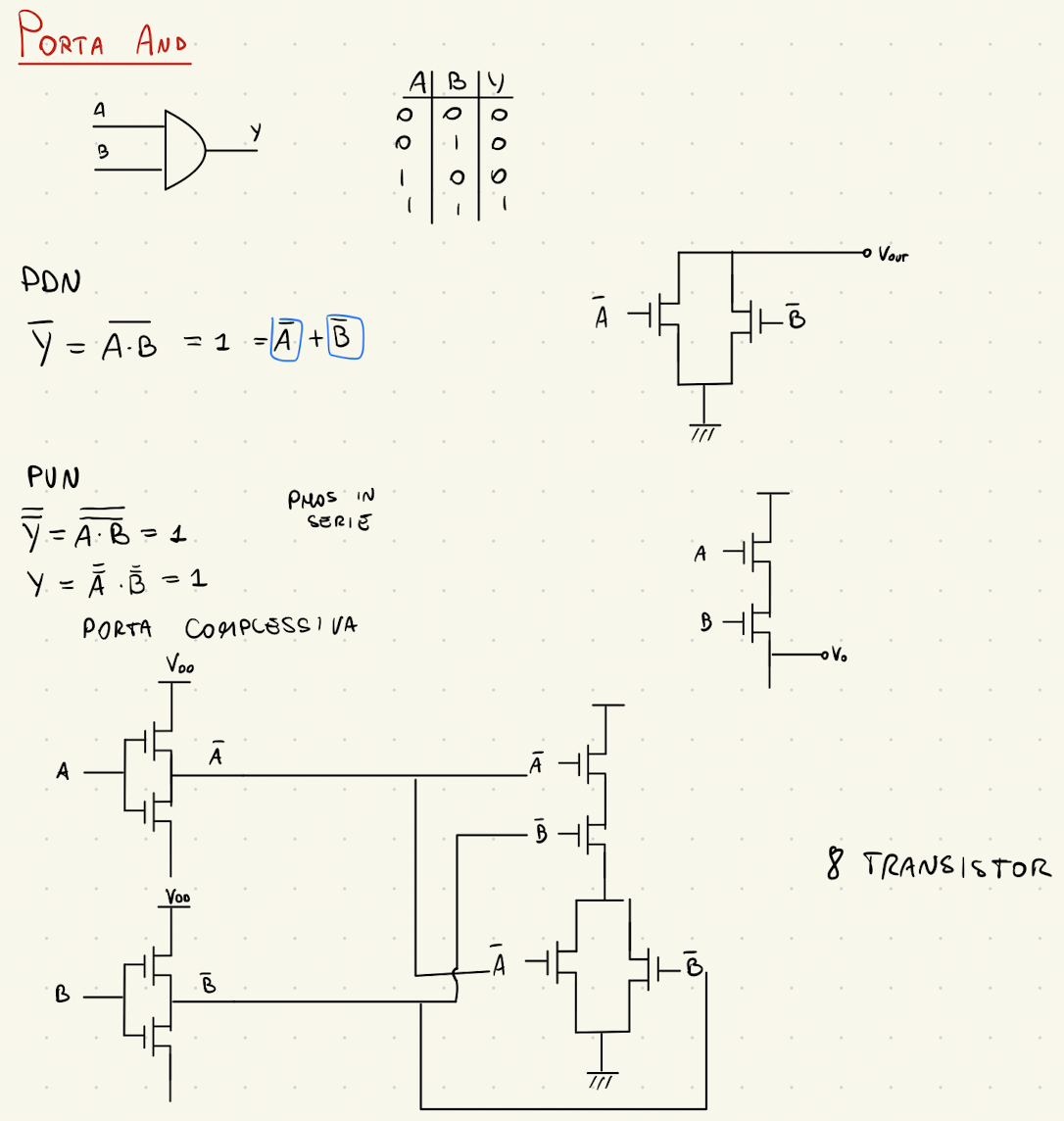

Iniziamo quindi dal progetto di una rete CMOS, cioè una rete logica fatta di transistor nmos e pmos, che implementa una porta logica qualsiasi, ad esempio una porta AND, OR, NAND, ecc...

La logica CMOS, o logica MOS Complementare, si basa su questo concetto: si progettano due reti, una che serve a portare l'uscita a 1(Vdd) e una che serve a portare l'uscita a 0(GND) spegnendo l'altra.Quindi quando sarà accesa una l'altra sarà spenta, ecco perchè logica complementare.La rete che porta l'uscita a GND è detta PULL DOWN NETWORK(PDN), quella che porta l'uscita a Vdd è detta PULL UP NETWORK(PUN).

Attenzione: l'espressione logica della PDN è y negato, perchè è la rete che porta l'uscita a 0, quindi se l'uscita è 1, la PDN è spenta.

Un secondo concetto essenziale è questo: la PDN è fatta di soli NMOS e la PUN di soli PMOS.L' AND tra due variabili si realizza con due transistor messi in serie(sia sulla PDN che sulla PUN, si progetta prima l'una e poi l'altra).L' OR tra due variabili si realizza con due transistor messi in parallelo(sia sulla PDN che sulla PUN)

Vediamo in pratica come si progetta una porta, per esempio prendiamo la AND, che ha espressione logica y = A•B. Conviene ovviamente progettare prima la PUN perchè y è la sua espressione già, invece la PDN ha l'espressione di y negato.

Tutte le altre porte derivano dalla combinazione di AND,OR e NOT.

Tornando alla nostra AND, la y la consociamo, ma y negato dobbiamo calcolarla: !y = !(A•B) che per la legge di De Morgan è !A+!B, quindi la PDN sarà fatta di due transistor nmos messi in parallelo, uno con gate A e l'altro con gate B.A e B perchè sappiamo che la PDN ha l'espressione di y negato, quindi se y è 1, la PDN è spenta, quindi A e B sono 0, quindi la PDN è accesa:

Qui siamo partiti dalla PDN, dalla sua espressione e poi l'abbiamo negata nuovamente per ottenere la PUN. In realtà, una volta che ho progettato la PUN, per ottenere la PDN o viceversa mi basta invertire: tutti i transistor che erano in serie diventano in parallelo e tutti quelli che erano in parallelo diventano in serie(AND diventa OR e OR diventa AND).

Abbiamo però bisogno di generare anche A negato e B negato, ecco allora che ci servono dei transistor in più per fare gli inverter. In genere nelle reti logiche si genera una sola volta per tutto il circuito l'ingresso negato, cosi lo faccio una volta sola senza sprecare transistor inutilmente, per un segnale già generato.

Poi c'è la logica Pass Transistor, molto semplice, consiste nel far "passare" i segnali attraverso i transistor, in pratica un and diventa cosi:

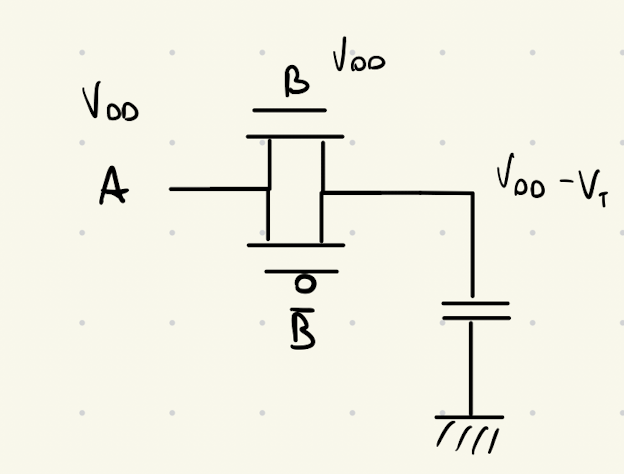

considerando che si devono generare anche i segnali negati, adesso servono 4 transistor. Ma in realtà c'è un trade-off: l'uscita alta(quando y=1 logico) non è più Vdd ma è Vdd-Vt.Questo in ogni porta PTL.

L'uscita in un circuito PTL, quando il transistor passante è acceso, non raggiunge mai la piena tensione di alimentazione Vdd, ma si stabilizza a un valore inferiore di Vdd - Vt, dove Vt è la tensione di soglia del transistor, dovuta al comportamento del passaggio del segnale attraverso il transistor.

Inoltre quando consideriamo la scarica di un condensatore, se c'è un PMOS dobbiamo considerare che la scarica non arriverà a 0 ma si fermerà a Vtp perchè sotto questa soglia il pmos si spegne.

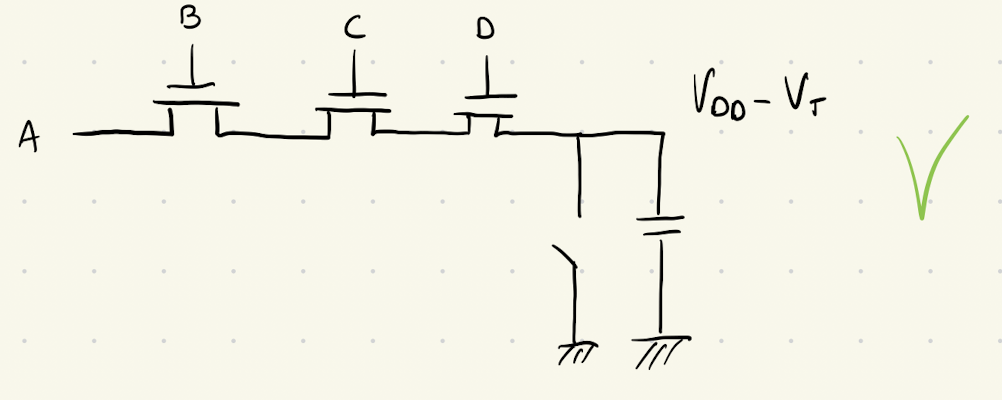

Un errore da non fare è connettere in cascata due porte PTL, perchè la tensione in uscita dalla prima non sarà mai Vdd, ma Vdd-Vt, quindi la seconda porta non riceverà mai un segnale a Vdd, ma a Vdd-Vt, quindi in uscita della seconda avremo Vdd-2Vt e cosi via. Piuttosto dobbiamo connetterle in questo modo:

Problema:

NMOS: Non può connettere bene a Vdd (alta tensione) quando il gate è basso, ma riesce a connettere a GND (bassa tensione) solo quando il gate è alto.

PMOS: Non può connettere bene a GND (bassa tensione) quando il gate è alto, ma riesce a connettere a Vdd (alta tensione) solo quando il gate è basso.

Quando un PMOS da solo controlla un nodo, non riesce a scaricare completamente un condensatore verso GND (si ferma a circa Vt sopra GND).

Soluzione: Il transmission gate combina un NMOS e un PMOS in parallelo, con i loro gate controllati in modo complementare. Questo consente una connessione completa sia a Vdd che a GND, permettendo di caricare e scaricare correttamente un condensatore o gestire segnali senza il problema di soglia.

Come ultima cosa vediamo prima un esercizio sull'analisi di una rete PTL dove dovremo scrivere la sua tabella di verità con i valori delle tensioni di uscita, il calcolo della potenza dissipata e la carica e la scarica dei condensatori nei circuiti con transistor per il calcolo dei tempi di proapgazione tramite unn esercizio completo. Prima introduciamo il concetto di alta impedenza.L'alta impedenza (o "stato ad alta impedenza") è una condizione in cui un componente elettronico, come un transistor, si comporta come se fosse scollegato dal circuito, non permettendo né il passaggio della corrente né l'applicazione di tensione. In pratica, in questo stato il componente ha un'impedenza molto elevata, e quindi non influisce sul resto del circuito.

In una porta logica, un transistor è in alta impedenza quando viene "disattivato" e non fornisce né un livello logico alto né basso all'uscita. Questo stato è utile, ad esempio, nei bus di dati condivisi, in cui più dispositivi possono collegarsi alla stessa linea: lo stato di alta impedenza consente a un dispositivo di "ritirarsi" per evitare conflitti, permettendo a un altro di controllare la linea.

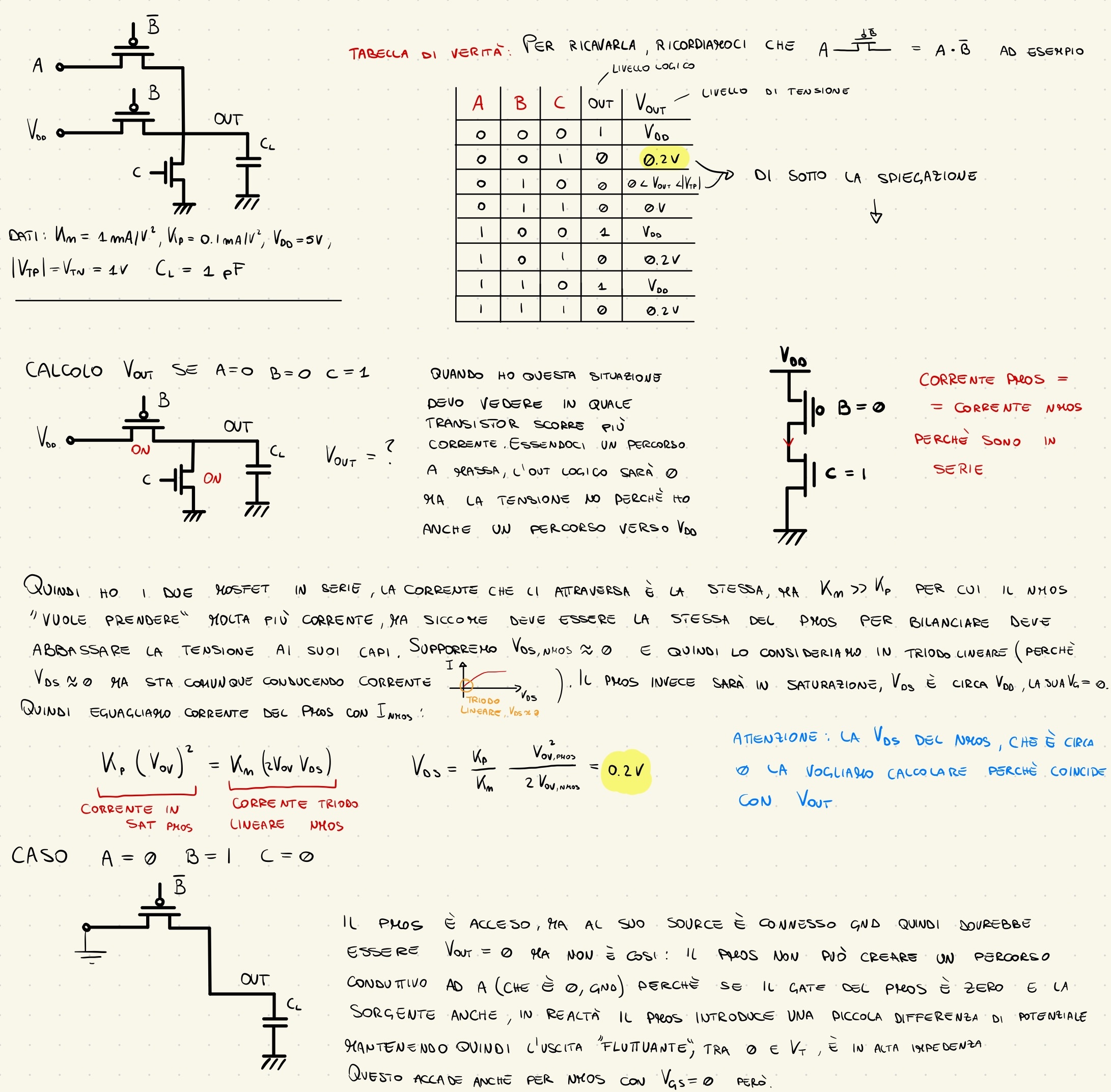

Quindi abbiamo A,B,C come variabili di input e una rete PTL di cui vogliamo conoscere l'uscita al variare delle combinazioni di A,B,C. Per prima cosa scriviamo la sua tabella di verità, ossia l'output al variare degli input forniti.

Trucco per compilare velocemente la tabella di verità sui i valori di input(tutte le combinazioni di A,B,C possibili): parto dalla variabile più a destra nella tabella, qui era C e scrivo 0 1 0 1 ... alternandone uno alla volta fino ad arrivare a scriverne 2^n, dove n è il numero di variabili, poi faccio lo stesso a sinistra ma alterno 0 e 1 ogni due, poi compilo la colonna di A e alterno 0 e 1 ogni quattro, e cosi via a potenze di due.

Ricordiamoci sempre che un pmos si accende quando il gate è a 0 e si spegne quando e a 1 e il nmos fa il contrario.

Poi calcoliamo la potenza dinamica e statica quando A=1,B=0 e C sia un'onda quadra tra 0 e Vdd a 1Mhz con duty cycle cioè il tempo in cui il segnale è in stato logico alto(1) al 50%:

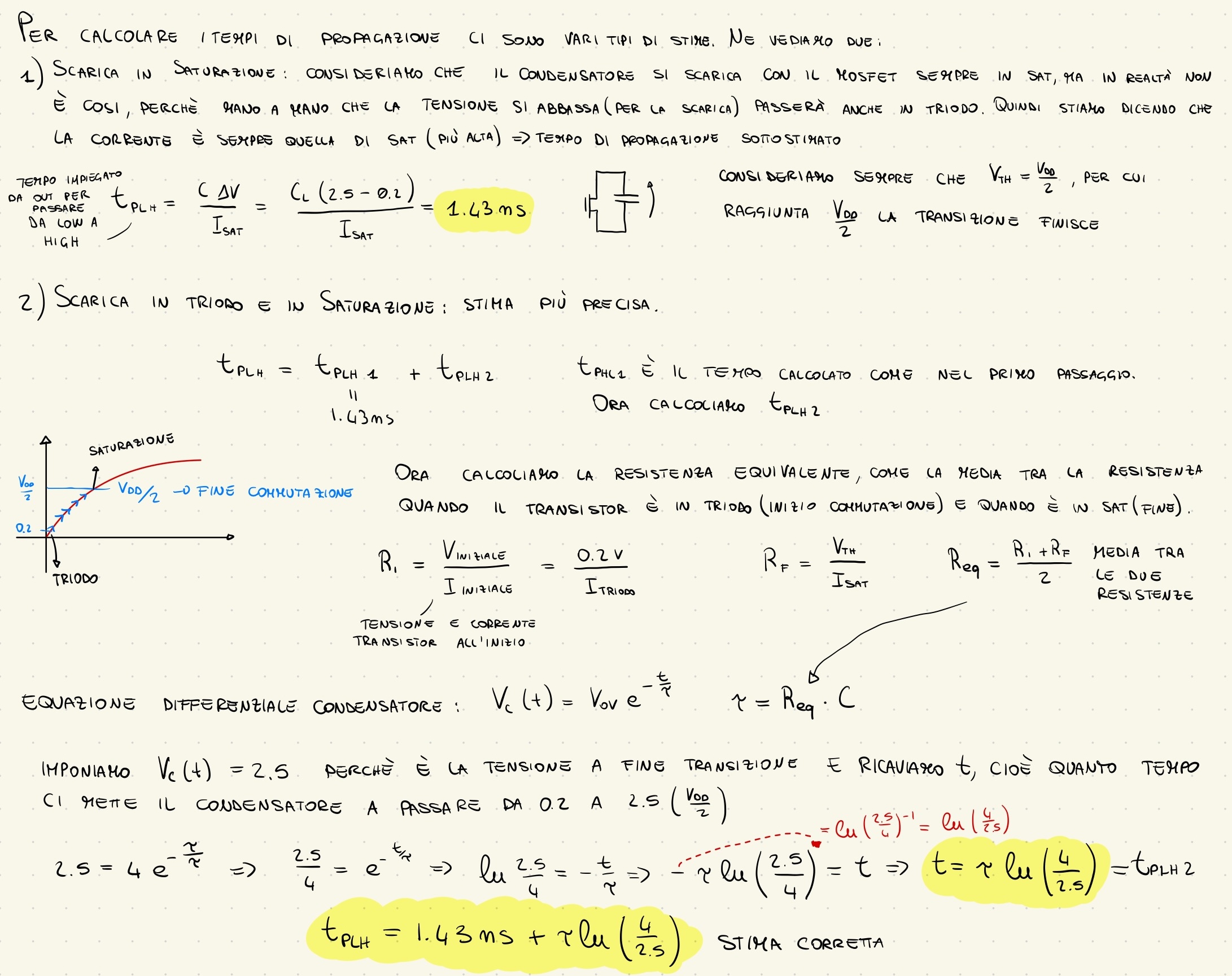

e per finire calcoliamo il tempo di propagazione:

quindi il secondo metodo permette di fare una stima più precisa del tempo di propagazione, ma è più lungo e complesso.Quindi abbiamo calcolato il tempo che la nostra uscita impiega a passare da 0 a 1 logico.E' del tutto analoga la procedura per calcolare il tempo per passare da 1 a 0.

Mi rendo conto che la trattazione può risultare molto complessa, specialmente per chi non è abituato a lavorare con equazioni differenziali e formalismi matematici di questo tipo, usate molto nei corsi di ingegneria.Se avete domande o dubbi, non esitate a contattarmi, sarò felice di rispondere a qualsiasi domanda o chiarimento.

© 2024 Edoardo Sorgentone. Tutti i diritti riservati.